In this article, I am going to talk about the definitions of setup time and hold time, as well as the calculation of circuit's performance limits where setup time and hold time should be considered.For digital sequential logic design, clock timing is the most critical problem to ensure functional corectness. Basically, the delay path between each pair of cascade registers decides the maximum clock frequency of this segment of circuit (unless special timing constraints applied). Due to the Buckets Effect, the worst delay path in the design became the most critical one (normally called as The Critical Path)that decides the highest frequency of the whole chip.

I. Definitions Of Setup & Hold Time

Prior to talking about setup time and hold time, I need to give a brief introduction about metastability.

You might have seen the ideal signal waveform in some simulation tools, such as Modelsim or VCS (Please don't tell me that you are using the simulation tool embedded in Quartus, because you should get rid of it right away). In the scope of an ideal digital signal sequence, the edges of the data switching and the sampling clock are perfectly alligned, and the data remains ideally steady during the whole clock cycle until the next clock sampling edge comes. However, this is not what really happen in the physical world.

In the real digital circuit, electronic signals need time to propogate through the logic gates. Registers are just like some checkpoints breaking down the combinational logics in slices through which the signals flow downwards. If a signal failed to reach the next checkpoint in a clock cycle, the information it carries will be lost. This is where our question comes from: What would happen if the signal arrive at the next register just on time?

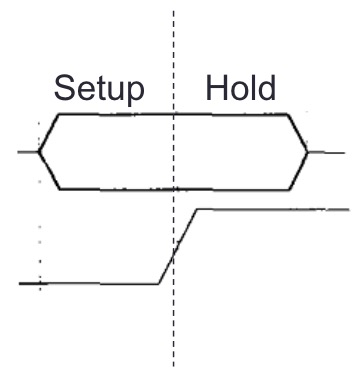

SETUP / HOLD TIME

The time window during which data are required to stay stable, setup time refers to the period before clock sampling, while hold time refers to the period after it.

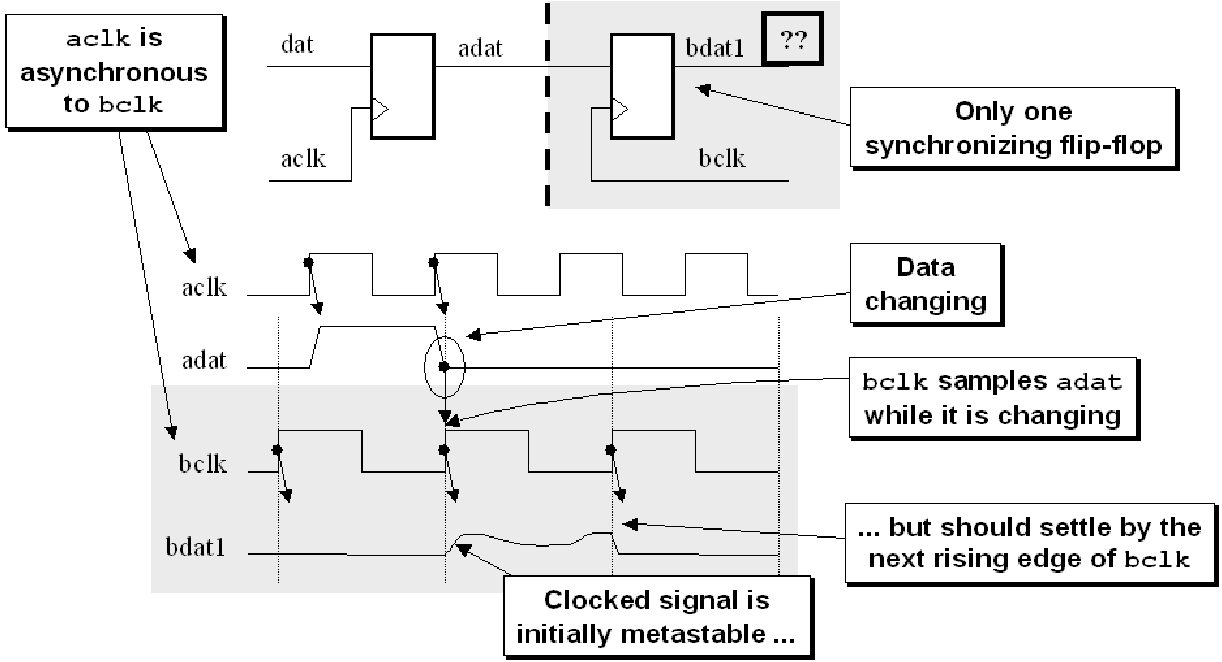

METASTABILITY

If the clock edge samples a data while it's changing, the sampled data are not assumed as either stable 0 or 1 state. Metastability can never be eliminated, normally we just isolate them in between of flip flops so that it will not go further beyond to mess up subsequent logic states.

"When sampling a changing data signal with a clock ... the order of the events determines the outcome. The smaller the time difference between the events, the longer it takes to determine which came first. When two events occur very close together, the decision process can take longer than the time allotted, and a synchronization failure occurs. "

Dally & Poulton

WHY IS METASTABILITY A PROBLEM

Since the CDC signal can fluctuate for some period of time, the input logic in the receiving clock domain might recognize the logic level of the fluctuating signal to be different values and hence propagate erroneous signals into the receiving clock domain.

MTBF (Mean Time Before Failure)

In many other articles, a simple 2-flip-flop synchroniser is introduced. However, even for such mechanism, there still lays possibilities for failure. The method to evaluate the circuit's capability to against such failure is to calculate its MTBF.

Theoretically, it is possible that for most simple 2FF synchroniser, the signal between the 2 flip-flops is still metastable before clocked into the target domain. MTBF is the expected time gap between two failures.

MTBF = 1 / fclk × fdata × X

Where X includes other factors, fclk is the receiving domain clock frequency, fdata is the speed of data change.

From the above partial equation, it can be seen that failures occur more frequently (with shorter MTBF) in higher speed designs, or when the sampled data changes more frequently.

English

English