如果说到“最受欢迎的数字RTL设计语言”,大部分来自北美的公司都会选择Verilog,而欧洲的同僚们都会支持VHDL。个人来说,我对Verilog的了解胜过VHDL。确切的说,我大概只能读懂VHDL代码而没有办法真的用它完成设计。所以如果在工作中不得不维护一份VHDL代码,我宁愿选择花点时间首先把它转化为Verilog,好过硬着头皮上手就干。你可能也有跟我一样的需求。那么怎么做才能更好的完成转化呢?本文中,我将跟大家分享一些个人经验。特别注意的是,本文的经验不仅仅可以用于把Verilog转化为VHDL,反过来也是一样的。

I. 工具和流程

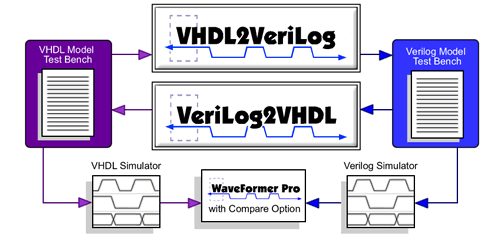

大致来说,我们完成这个过程一共需要三个步骤。

首先,我们要准备好需要被转化的源代码。在这个阶段,我们最好是先把所有的VHDL源文件都编译一下,确保源文件依赖的所有package文件或者宏定义都是齐备的,所有的代码都是没有语法问题的。有条件的情况下,最好还是搭建一个测试平台,把VHDL代码的基本功能验证一下,确保功能是正确的。

第二个步骤就是完成语言转化。在这个阶段,你需要用到一个叫SynaptiCAD的EDA工具,然后调用他内嵌的HDL Translators工具箱来完成翻译工作。请注意,从官网下载的软件在免费试用版license前提下是可以使用所有功能的,但是对于单文件代码长度有1000行的限制。所以如果代码比较长的话,大家还是要想办法搞到完整的license。

最后一个步骤就是验证。而这里说的验证,并不是直接一上来就用第一个步骤中提到的验证平台进行功能性的验证。我推荐大家在功能验证之前,首先对两份代码进行一次形式验证。目前业界有两款主流的形式验证工具,一个是Synopsys的Formality,另外一个是Cadence家的LEC。你可以从这两款工具中任选一款来完成VHDL和Verilog代码的形式验证,但我强烈推荐大家同时交叉混合使用这两款工具。因为在比对过程中难免会遇到一些奇怪的问题,因为报错信息不友好迟迟找不到问题所在,这种情况下果断换用另外一款工具通常都能起到意想不到的效果。

II. 步骤一:准备文件

在真正开始HDL代码转化之前,最好是先确保源代码的完整性和正确性。为了验证这一点,你可能需要搭建一个简单的测试平台,编写一些基本的激励程序来驱动模块输入端,并观察输出响应是否正确。如果你没办法保证你的代码都是用同一种语言写的(例如说,因为你自己只会写Verilog,那么有可能你的待测模块和测试平台分别是用VHDL和Verilog写的),那么你可能就需要参考本博的另外一篇文章。

English

English