It is said that, when it comes to the favourite digital RTL design language, most companies in the North America prefer Verilog, whereas many of their European counterparts will choose VHDL. Personally, I know Verilog better than VHDL. More specifically, I could only read VHDL code but not write it. So if I need to modify a code written in VHDL, I'd prefer to convert it to Verilog prior to starting any bit of amendment. You might have the same need too. Then what is the best way to reach this goal? In this article, I'd love to share some personal experience about this. Please note that the method I'm going to introduce to you in this article not only can convert code from Verilog to VHDL, but also do it in the other way round.

I. Tools And Procedure

Basicly, we have three steps to go before we get the job done.

First of all, prepare source files. At this stage, we need to compile all VDHL design files, to make sure that all neccessary packages or definition macros do exist and all syntax errors are already cleared. You are even suggested to run a test to the design to ensure that it is functional correct.

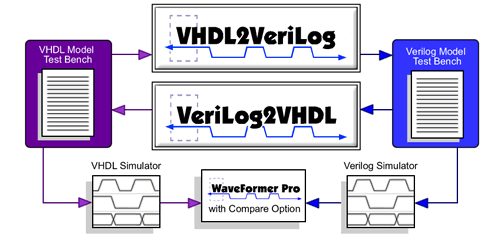

The next step will be the conversion process. At this stage, you will need to install a EDA tool named SynaptiCAD and use its embedded HDL Translators to finish the language translation. Please note that you could apply for a evaluation version of it from their website, but a code length limit of 1000 lines in a single file is applied unless you could get a license.

The last step is verification. Before you run any functional verification to the new verilog design, I suggest you to take a formality verification in advance. There are two dominating tools designated for formality verification, namely Formality from Synopsys, or LEC from Cadence. You can pick either of them to finish this part, but what I wanna suggest you is that, try mixing usage of both tools, for you might encounter many triky problems, and each tool has its drawbacks. Try to use another tool instead when you get stuck.

II. Step1: Preparation

Before you start the HDL conversion, it is good to make sure that the source code is complete and error-free. To verify it, you should build a simple testbench and create some stimulus to its inputs and probes to its outputs. If you have problem constraining you code (both DUT and testbench) in a single language (Say you can only write your testbench in Verilog or SystemVerilog, but the DUT is written in VHDL), you can try to mix them up by following the method introduced in this article.

中文

中文